基本信息

- 项目名称:

- 基于可逆逻辑的计算机系统原型(Recom-II)

- 来源:

- 第十二届“挑战杯”省赛作品

- 小类:

- 信息技术

- 大类:

- 科技发明制作A类

- 简介:

- 设计了一种基于可逆逻辑的可逆计算机系统原型Recom-II。利用可逆逻辑门代替传统逻辑门完成整个计算机系统原型的设计,该原型机可以完成中央处理单元基本功能。将系统植入FPGA芯片,硬件验证了原型机的功能和正确性。 Recom-II通过重用逻辑信息位,减少了因信息位丢失而产生的能量损耗。通过Virtuoso系统验证了Recom-II的组成部件--可逆全加器能够降低94.8%的功耗。

- 详细介绍:

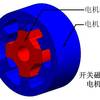

- 本作品提出并实现了一种基于可逆逻辑的可逆计算机系统原型Recom-II。使用可逆逻辑门作为逻辑器件完成整个计算机系统原型的设计。该原型机由可逆算术逻辑单元、可逆微程序控制器、可逆程序计数器、可逆时许发生器以及一系列可逆寄存器组成,可以完成计算机中央处理单元基本功能。设计中,使用可逆逻辑门完全取代传统逻辑门,通过重用逻辑信息位,减少逻辑信息位的消耗和丢失,从而降低能量的损耗,实现低功耗。 传统的不可逆逻辑运算会会引起一个信息位能量损耗,而Bennett提出了传统计算机中的每步操作都可以改造为可逆操作,使得两者具有完全相同的计算能力和计算效率。基于可逆逻辑的可逆计算机系统原型就是在这些理论的基础上出来的,对一部分信号量进行重新利用,减少能量的损耗。 将使用可逆逻辑设计的各个部件相连,构成整体的计算机系统原型,为此原型机设计指令系统与微指令系统,使其可以完成中央处理单元的功能。 本作品使用了两种方法来验证可逆计算机系统原型的正确性。第一种是通过C++语言编程来模拟原型机的电路设计,通过变量的数值变化表示电路的电位变化,通过赋值表示电路连接,模拟结果验证了原型机的各个部件的正确性。第二种是通过Quartus软件模拟电路连接的方法,设计出具有可逆逻辑门相同功能的"黑盒"芯片,直接使用“黑盒”芯片来完成电路连接,并通过数据变化的波形图来验证原型机各个部件及整个系统的功能的正确性。仿真结果表明,Recom-II中的各个部件均可准确地完成其特定的功能,并且可逆计算机系统原型完全可以实现中央处理单元的功能。 在使用Quartus软件完成了编译和仿真验证后, 将其程序下载到FPGA芯片中,完成了可逆计算机系统原型从设计到软件仿真到硬件验证过程。 在Virtuoso环境下,采用PMOS、NMOS并联传输门结构构成Feynman、Toffoli逻辑电路,并构建一位全加器,验证可逆逻辑结构降功耗的效果。 可逆计算机系统原型的提出对可逆逻辑应用于电路设计的发展有着重要的意义。鉴于可逆逻辑在降低功耗上的优越性,在未来的集成电路设计中必将有广泛的应用,随着硬件水平的提高,工艺与材料对可逆逻辑电路的制约也将随之降低。届时,本文提出的可逆计算机系统原型会在未来计算机的设计中有着极有意义的参考价值。

作品专业信息

设计、发明的目的和基本思路、创新点、技术关键和主要技术指标

- 设计、发明的目的: 1.设计基于可逆逻辑的计算机系统原型; 2.验证可逆原型机的可行性、正确和功能; 3.验证可逆原型机低功耗性能; 4.为低功耗可逆计算的发展提供依据。 基本思路: 1.使用基本可逆逻辑门构建可逆电路; 2.设计可逆全加器,算术逻辑运算单元,程序计数器、时序产生器等逻辑部件。按照可逆逻辑部件构建可逆计算机系统; 3.利用C++语言对系统进行正确性和功能性验证; 4.采用QuartusII对电路进行仿真; 5.通过QuartusII软件和DE2实验电路板,将逻辑部件构成一个8位运算的计算机系统原型写入FPGA上; 6.在Virtuoso环境下,采用PMOS、NMOS并联传输门结构构成Feynman、Toffoli逻辑电路,并构建一位全加器,验证可逆逻辑结构降功耗的效果; 创新点: 1.利用可逆逻辑实现计算机功能部件,与传统的逻辑设计有着根本不同; 2.通过重用信息位,避免因信息位丢失而损失能量。与传统的低功耗电路设计方法有本质不同; 3.传统的可逆逻辑应用于量子计算,本作品把可逆逻辑应用于电子电路 技术关键: 1.Recom-II各个部件(如可逆算术逻辑单元)的可逆设计与实现; 2.系统功能性和正确性的验证; 3.基于FPGA的可逆逻辑部件的实现; 4.可逆电路低功耗运行的验证; 5.可逆原型机的时序控制; 技术指标: 内部数据总线位数:8位 微指令数:21条 可逆门数:1039 功耗降低比分比:90%以上

科学性、先进性

- 本作品实现的可逆原型计算机完全建立在可逆逻辑设计的基础上,能够完成计算机中央处理单元的基本功能。使用电子电路的方法实现可逆逻辑设计,降低电路的功耗。 实验结果表明:可逆逻辑实现的全加器(FA)比不可逆逻辑的电路能耗降低了94.8%。 目前国内外现有的技术主要实现单个的可逆逻辑器件,还没有设计出整体的可逆计算机系统。

获奖情况及鉴定结果

- 2009.10, 《基于PNC级联系统》 南通市“天翼杯”本科组编程大赛荣获特等奖。 2010.4,论文《基于可逆函数复杂性的正反控制门可逆网络综合》,发表于《计算机科学》杂志社。 2010.6,论文《Using New Designed NLG Gate for the Realization of Four-bit Reversible Numerical Comparator》 发表于ICENT 2010 2010.7论文《Function Modular design of the DES encryption system based on reversible logic gates》发表于MEDIACOM 2010,IEEE computer society

作品所处阶段

- 实验室阶段

技术转让方式

- 无

作品可展示的形式

- 模型、图纸、现场演示、图片、样品

使用说明,技术特点和优势,适应范围,推广前景的技术性说明,市场分析,经济效益预测

- 1、技术特点和优势: ① 低能耗: 在计算机进行算术/逻辑运算时,因为信息位的丢失会产生能量的损失,基于可逆逻辑设计思想,可以减少这部分信息位丢失而差生的能量。可逆逻辑实现的全加器(FA)比不可逆逻辑的电路能耗降低了94%。 ②易于扩展: 随着计算机硬件的发展,计算机处理的字长会越来越多,本作品目前以8位作为运算单元,从原理上可以扩展到任意字长。 ③实现电路代价小: 在设计过程中,最大限度的使用可逆门输出端的信号,从而减少了可逆逻辑门和垃圾输出的个数,使得电路在实现时代价特别小。 2、适应范围: 完成一般计算机的相关功能。 3、应用前景: 可逆计算机系统原型的提出对可逆逻辑应用于电路设计的发展有着重要的意义。鉴于可逆逻辑在降低功耗上的优越性,在未来的集成电路设计中必将有广泛的应用,随着硬件水平的提高,工艺与材料对可逆逻辑电路的制约也将随之降低,届时,本作品提出的可逆计算机系统原型会在未来计算机的设计中有着极有意义的参考价值。

同类课题研究水平概述

- 在过去的30年里,Feynman,Fredkin以及Toffoli等人已提出了很多基本的可逆逻辑门。已有许多学者利用各种综合方法,将这些门以级联的形式构建可逆逻辑门网络,来减少常量输入数及无用输出数。例如:Hafiz Md. Hasan Babu等人设计的全加器(FA)、Masoumeh Shams等人设计的乘法器、Himanshu Thapliyal等人设计的触发器,Frank设计了一种4位可逆运算单元。 目前国外现有的技术主要实现单个的可逆逻辑器件,诸如:全加器,触发器、除法器、比较器等,还没有设计出整体超过8位的可逆计算机系统。