基本信息

- 项目名称:

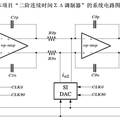

- 基于65nmCMOS用于3G WCDMA接收器的高速低功耗连续时间ΣΔ调制器

- 来源:

- 第十一届“挑战杯”国赛作品

- 小类:

- 信息技术

- 大类:

- 科技发明制作B类

- 简介:

- 本课题完成了一种移动通信接收器中的调制器的设计。此设计应用于3G WCDMA通信标准中。在本设计中使用了一种新型的SCSR反馈电路,同时运用了当今最先进的模拟集成电路工艺¬——65nmCMOS,最终本设计具有高速、高分辨率、低功耗以及小体积的特点。

- 详细介绍:

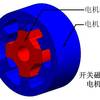

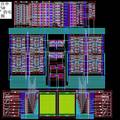

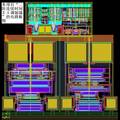

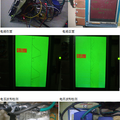

- 本课题所设计的基于65纳米CMOS工艺连续时间ΣΔ调制器可应用于3G WCDMA通信标准中。WCDMA技术为目前应用最广泛的3G标准,而其较传统的2G标准来说具有更广的信号带宽。这也就对当今的移动通信设备接收器的系统带宽提出了更高的要求,传统移动接收器的带宽已无法满足3G标准。目前移动通信产业的硬件发展面临了新的技术革新,当今市场上也新出现了许多不同品牌不同功能的3G手机。3G技术的发展要求3G WCDMA接收器中的模数转换系统具有更高的信号带宽,而通常此类模数转换器是由Sigma-Delta调制器来实现的。传统的Sigma-Delta调制器虽然可以提供较高的输出信号分辨率,但其信号带宽却受到了过采样技术本身的制约,故传统Sigma-Delta调制器目前难以应用于高带宽通信标准中。 基于以上考虑,我们设计了具有更高带宽的连续时间ΣΔ调制器。在系统的设计中,我们充分考虑了连续时间ΣΔ系统所面临的非理想因素影响,并且选择了合适的结构及技术来对系统性能加以完善。在克服连续时间ΣΔ调制器中最难以解决的瓶颈——反馈DAC的时钟抖动噪声,我们应用了最为先进的DAC反馈脉冲改进技术——开关电容开关电阻结构。本课题所设计的连续时间ΣΔ调制器可提供12比特的高分辨率,其信噪失真比可达66.7dB。调制器的信号带宽可达2MHz,系统的时钟速度为250MHz。本设计采用当今最先进的模拟集成电路工艺¬——65nmCMOS,其总功耗在5.3mW之内。其电路部分的版图面积为0.031mm2. 该项目的设计采用了自上而下的设计方式:理论分析——系统建模——电路设计——版图设计。目前该项目已完成实验室电路仿真及版图设计工作。

作品专业信息

设计、发明的目的和基本思路、创新点、技术关键和主要技术指标

- WCDMA技术为目前应用最广泛的3G标准,较传统2G标准来说具有更广的信号带宽。传统移动接收器的带宽已无法满足3G标准。3G技术的发展要求3G WCDMA接收器中的模数转换系统具有更高的信号带宽,而通常此类模数转换器是由Sigma-Delta调制器来实现的。传统的Sigma-Delta调制器虽然可以提供较高的输出信号分辨率,但其信号带宽却受到了过采样技术本身的制约,故传统Sigma-Delta调制器目前难以应用于高带宽通信标准中。基于此考虑我们设计了具有更高带宽的连续时间ΣΔ调制器。 该项目的设计采用了自上而下的设计方式:理论分析——系统建模——电路设计——版图设计。设计中,我们充分考虑了连续时间ΣΔ系统所面临的非理想因素影响,并且选择了合适的结构及技术来对系统性能加以完善。在克服连续时间ΣΔ调制器中最难以解决的瓶颈——反馈DAC的时钟抖动噪声,我们应用了最为先进的DAC反馈脉冲改进技术——开关电容开关电阻(SCSR)结构。本课题所设计的连续时间ΣΔ调制器可提供12比特的高分辨率,其信噪失真比可达66.7dB。调制器的信号带宽可达2MHz,系统的时钟速度为250MHz。本设计采用当今最先进的模拟集成电路工艺¬——65nmCMOS,其总功耗在5.3mW之内。其电路部分的版图面积为0.031mm^2.

科学性、先进性

- 传统的移动通信接收器受其自身技术原理的限制,难以实现更高的信号带宽.本项目的设计基于连续时间系统架构,使调制器可能达到的信号带宽较传统技术有了较大的提升, 连续时间ΣΔ技术也是基于传统的离散ΣΔ技术所发展而来,是目前ΣΔ技术的发展方向.然而连续时间ΣΔ调制器会受到其反馈数模转换器(DAC)中时钟抖动所造成的反馈信号误差的影响,导致系统性能下降,这也是一直以来连续时间ΣΔ技术中的一个难以解决的瓶颈。本设计采用了一种新型反馈DAC结构,使得反馈脉冲波形对于时钟抖动的敏感度大大降低的同时,又保证了反馈电流的峰值不会过高。解决了在连续时间ΣΔ调制器中时钟抖动敏感度与反馈电流峰值之间难以平衡折中的问题。此外本设计采用了65nm CMOS工艺,这在目前模拟集成电路的设计与实现中都是非常先进的。65nm工艺不仅可以减小集成电路的体积,使得电子产品的便携性得到提升,同时也使系统的电源电压降低,减少功耗。

获奖情况及鉴定结果

- 该项目在IEEE澳门大学学生分会所组织举办的“IEEE科研项目竞赛2009”的比赛中获得冠军。

作品所处阶段

- 实验室阶段

技术转让方式

- 可与有兴趣厂商洽谈技术转让细节

作品可展示的形式

- 图片,文字介绍

使用说明,技术特点和优势,适应范围,推广前景的技术性说明,市场分析,经济效益预测

- 本项目基于连续时间系统架构进行设计,使移动通信接收器中的调制器具有更高的信号带宽。在电路实现上采用新型SCSR反馈DAC,有效地减小了DAC中时钟抖动对系统性能的影响。本设计采用先进的65nm CMOS工艺,减小了芯片面积及系统功耗。本项目选取并采用的系统结构简明、易于理解实现。设计中考虑周详,对非理想因素进行了有效地解决。采用工艺先进,符合目前“便携、省电”的移动通信设备的发展趋势。较传统设计而言,本项目采用的结构使系统性能有了理论性的提升,应用先进的材料工艺使本设计的体积及功耗从实质上超越传统产品。 本项目的设计目标是使3G WCDMA标准下的移动通信接收器中的调制器具有更高的带宽、更好的分辨率以及更低的功耗和体积。本项目主要适用于WCDMA移动电话,亦可用于MP3、MP4等多媒体播放器。 此项目技术在目前的同类技术中结构新颖,理论完整,综合性能优秀。具有较好的技术前景。考虑到目前3G标准的盛行,3G硬件设备的要求也越来越高,本项目具有良好的市场前景及经济效益。

同类课题研究水平概述

- 连续时间Sigma-Delta调制器作为一种基于传统离散时间Sigma-Delta调制器的改进技术,已成为当前较先进的过采样模数转换技术,其将是Sigma-Delta模数转换设计的发展方向。国内目前关于连续时间Sigma-Delta调制器设计的论文数量较少,多数博士论文及学术期刊着眼于传统离散时间Sigma-Delta调制器的结构分析与性能改进,以及带通Sigma-Delta调制器研究。近年来,在代表着国际集成电路最高水平的IEEE国际固态电路会议(ISSCC)上,连续时间Sigma-Delta调制器设计的论文数量已经出现了大幅的增加,然而目前已有的大多数相关的高水平会议论文都着眼于连续时间Sigma-Delta系统中量化器的设计以及环路滤波结构的研究改进,而对于反馈环路中数模转换器的时钟抖动影响的研究却为数甚少。本课题正是基于简化结构、降低功耗、确保性能的考虑,对反馈数模转换器(DAC)的输出脉冲波形进行改进,以减小系统受DAC中时钟抖动的影响。 此外,小体积、低功耗是当今的移动通信设备发展的总体趋势。本设计基于上述考虑,采用了目前模拟集成电路工艺中最先进的65nm CMOS工艺。目前,国内的集成电路研究所采用的工艺都相对较大,全国部分重点高校研究所采用的半导体工艺为0.5μm,行业设计中的常见的工艺有90nm、180nm以及0.35μm。从目前高水平的国际固态电路会议中可以发现,大多论文的研究也是基于90nm及180nm工艺。相比目前应用最普遍的90nm及180nm,本设计的芯片体积及功耗将会得到明显的减小。