作者:2017级本科生 钟宏涛 电子工程系

指导老师:李学清 电子工程系

关键词:低功耗、嵌入式动态存储、纳米继电器、更长的保留时间、一步刷新

摘要

如今,嵌入式动态存储(eDRAM)需求量越来越大。与内存不同,eDRAM与处理器集成在一起,因此可以带来更高带宽以及更小面积,在很多领域如物联网、传感、边缘计算等都有着广泛的应用。其中,三晶体管嵌入式动态存储(3T eDRAM)凭借其良好的集成性以及适中的单元面积和速度备受青睐。然而,由于3T eDRAM需要通过刷新来保持数据,而随着阵列规模的增大,刷新操作会消耗大量的能量并严重影响性能。本工作利用纳米继电器(NEM Relay)的优良特性并提出了两种方案来解决3T eDRAM刷新带来的问题。第一种利用NEM Relay作为写晶体管减小漏电,可以极大降低刷新能耗甚至可以针对特殊应用进行优化实现非易失。第二种利用NEM relay作为存储晶体管以延长数据保留时间,并提出一步刷新策略,可以极大降低刷新带来的能耗和阻塞问题,并且延长设备使用寿命。

纳米继电器

NEM Relay是一种与CMOS集成性良好的器件,可以有3个、4个甚至5个端口。NEM Relay有很多良好的特性,如关断状态漏电极低、成熟的工艺等,其中4T NEM Relay甚至可以分离读操作和写操作,因此没有阈值压降。由于这些良好的性质,NEM Relay广泛出现在传感、存储以及可编程逻辑阵列等应用中。

图片1 纳米继电器

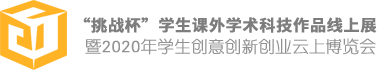

纳米继电器作为写晶体管的2T1N/C eDRAM (DATE 2020)

刷新操作源于电荷泄漏。3T eDRAM主要有三个漏电路径:通过写晶体管(最多)、通过存储晶体管栅极以及通过源漏处的反偏PN结(最少)。该工作利用NEM Relay关断状态漏电极低的特性可以有效抑制通过写晶体管的漏电,进而延长数据保留时间以及降低刷新功耗。在一些对低功耗有特殊需求的场景甚至可以使用厚栅晶体管来减少通过存储晶体管栅极的漏电,将数据保留时间延长到年,实现几乎非易失。

图片2 纳米继电器作为写晶体管的2T1N/C eDRAM

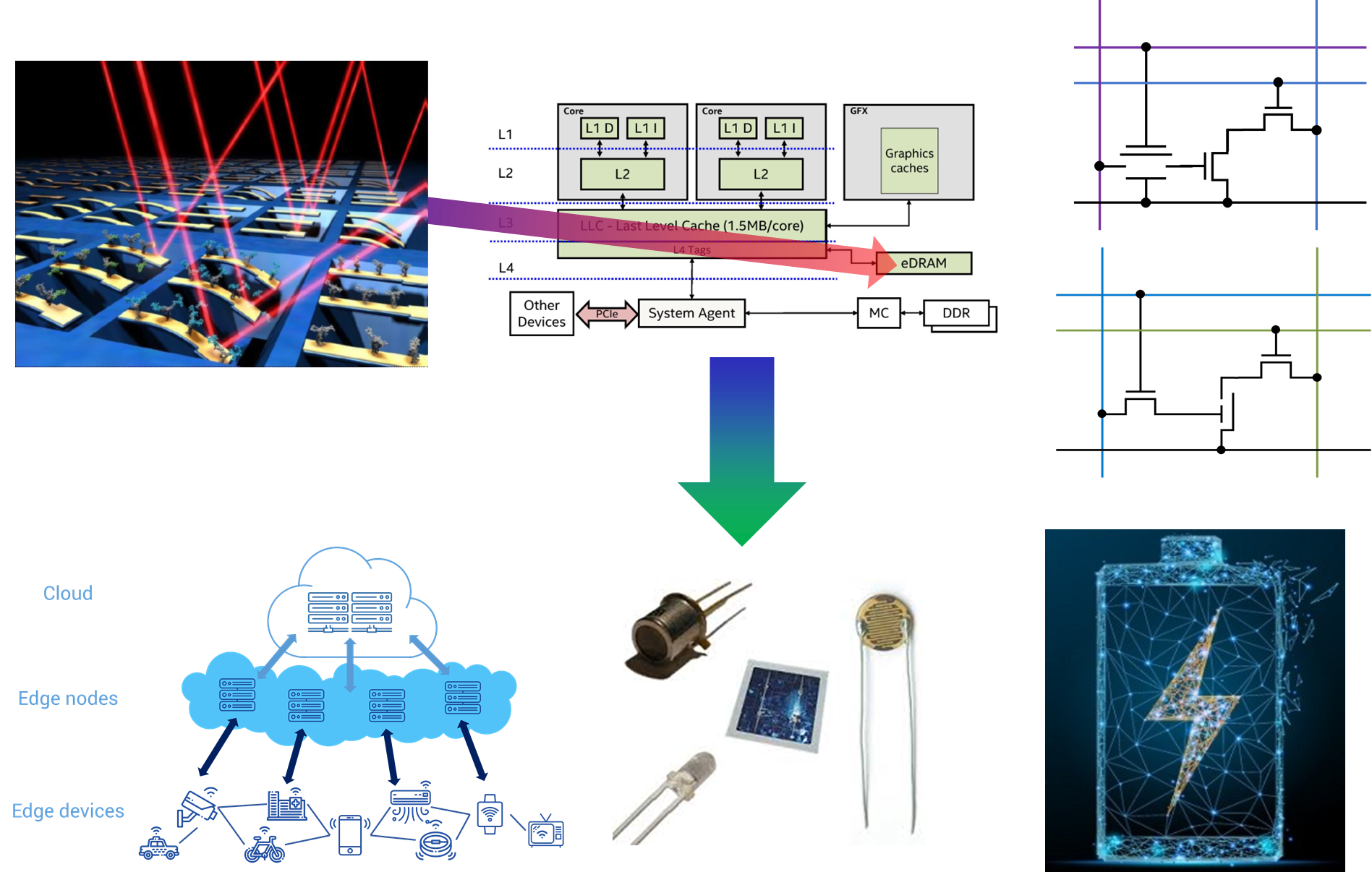

纳米继电器作为存储晶体管的2T1N/C eDRAM (TCAS-II)

如果用NEM Relay作为存储晶体管,可以利用NEM Relay的滞回特性来延长数据保留时间,同时可以使用全新的one-shot refresh让刷新‘0’和刷新‘1’所使用的方法一样。这样做有几个好处:1)可以省去原来刷新操作所需要的读操作;2)将刷新从逐行刷新变成全阵列一起刷新,缩短了刷新时间;3)极大降低了刷新功耗;4)极大减小了刷新对正常读写访问带来的阻塞,极大地提高了eDRAM的性能。

图片3 纳米继电器作为存储晶体管的2T1N/C eDRAM