基本信息

- 项目名称:

- 14位200M ADC设计与实现

- 来源:

- 第十二届“挑战杯”省赛作品

- 小类:

- 信息技术

- 大类:

- 科技发明制作B类

- 简介:

- 本作品利用0.13μm CMOS工艺,数模混合设计并实现了一个14位200M的流水线模数转换器(ADC)。

- 详细介绍:

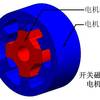

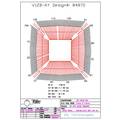

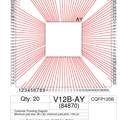

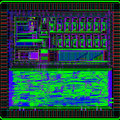

- 本作品设计并实现了14-bit 200MS/s流水线模数转换器(ADC),达到国内先进、国际一流水平。与传统的流水线ADC相比,该设计没有采样保持电路,节省了大量功耗和芯片面积;采用数字校准技术对模拟电路的线性、非线性误差和失调进行校准,能够容忍更大的模拟电路误差,并且采用后台校准技术跟踪ADC的工作情况,保证了作品在不断变化的温度、工艺、电压等环境下的稳定性;考虑到高速的运放的特性,采用了低抖动时钟技术,进一步提高了信噪失真比(SNDR)。最后,在0.13μm CMOS工艺下实现了基于BLMS校准算法的高速高精度流水线ADC,在1.2V电压下,功耗约为500mW,面积约为20mm^2。联合仿真结果显示,在83MHz输入信号下,有效比特位(ENOB)达到了12.3位。目前测试工作正在进行中。

作品专业信息

设计、发明的目的和基本思路、创新点、技术关键和主要技术指标

- 一、设计目的: 近年来,随着通信技术的高速发展,高速高精度的模数转换器(ADC)的需求日趋明显,并受到了广泛的关注。 国际上的ADC的技术已经达到了16位 250MS/s,为推动国内相关领域技术的发展,本次设计并实现了一个14位 200MS/s的ADC。 二、基本思路: 该ADC采用低功耗的流水线结构,并利用数字校准的技术改善其性能。在此设计中,考虑到其200MHz的高采样率,运放非线性和时钟抖动等误差都进行了校正。 三、创新点: 1.基于Blind LMS算法的数字后台校准技术; 2.高线性度低增益运放; 3.低功耗流水线ADC。 四、技术关键: 1.数字后台实时校准; 2.非线性误差校准; 3.校准DAC和流水线ADC输入级无S/H设计; 4.高速高线性度运放设计; 5.低抖动时钟设计。 五、主要技术指标: 有效位数(或信噪失真比),采样速率,无杂散动态范围,积分非线性误差,微分非线性误差。

科学性、先进性

- 本作品设计并实现了14-bit 200MS/s流水线ADC,达到国内先进、国际一流水平。该设计没有采样保持电路,节省了功耗和芯片面积;采用实时的数字校准技术,保证了作品在不断变化的温度、工艺、电压等环境下的稳定性;考虑到高速的运放的特性,采用了低抖动时钟技术。最后,在0.13μm CMOS工艺下实现了基于BLMS校准算法的高速高精度流水线ADC。

获奖情况及鉴定结果

- 无

作品所处阶段

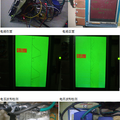

- 流片成功,样片

技术转让方式

- 协商确定

作品可展示的形式

- 实物、样品

使用说明,技术特点和优势,适应范围,推广前景的技术性说明,市场分析,经济效益预测

- 数字信息系统需要高速、高精度的ADC来提高其性能。例如,LTE-Advanced、802.16m等4G无线通信系统中,要求基站向高宽带、高采样率、多通道、多输入/输出天线(MIMO)等方向发展,应用正交频分复用(OFDM)的调制方式和MIMO等技术,对系统下行接收信道中采用的ADC的分辨率和速度都提出了更高的要求,甚至需要达到14-bit, 200MS/s(采样率)的性能。另一方面,消费类电子、医疗生物等电子领域需要降低功耗来延长其寿命,这就进一步对ADC提出了低功耗的需求。高速、高精度和低功耗的要求,是ADC设计的主要难点。

同类课题研究水平概述

- 随着高速数据通信、软件无线电、雷达和卫星通信等领域的长足发展,以及数字信号处理技术的成熟和完善,ADC的性能已经成为制约数字通信系统性能的关键模块。高速、高精度ADC的设计和实现将是未来发展新型通信系统的瓶颈和研究重点。ADC在电子信息系统中的必要性和重要性,以及其实现的难度,使其一直成为国内外学术界和工业界追捧研究的热点。 目前,国际上产业界设计和实现的ADC已经达到16位250MS/s甚至更高速度,学术界则着重于更低电压、更低功耗的高性能ADC设计和实现。相比于产业界,学术界实现的高速、高精度ADC已经能够达到几百毫瓦甚至更低,其品质因数(FOM)已经接近或者达到100fJ/conv。 在工业界,ADI、TI、Maxim、Linear、NXP等公司走在生产和研发ADC的前列。在国际学术界,MIT、U.C. Berkeley、Oregon State University、Stanford、IMEC等大学和机构在这一领域的研究一直处于国际领先水平。国内主要有复旦大学、清华大学、东南大学、电子科技大学、华为公司等在研究设计ADC。 目前,在IEEE核心论文和国际核心期刊上,采用低功耗设计和数字校准技术的ADC可以达到从10到16位的精度,从20M到500MS/s的速度。国内自主研发的ADC也可以达到12位40MS/s的高水平,因此,国内ADC技术的发展还有很大的前景,在国内展开有关高性能和低功耗的ADC的研究,将有助于提高国内在此领域的研发水平。 很高精度(≥ 20-bit)的ADC多由Δ-Σ ADC实现,但是其速度很难提高;Flash ADC速度最快,但是其功耗和芯片面积随着精度呈指数增加,从而限制了其精度的提高;算法型(SAR) ADC功耗极低,适用于生物医疗电子,并且随着今年来的发展,其速度和精度得到大幅度提高,分别实现了10-bit 100MS/s和18-bit 12.5MS/s;流水线ADC能够达到比较高的精度和速度,有可能实现高速、高精度ADC,不过业界设计的流水线ADC的功耗通常很高,有很大的改进空间。